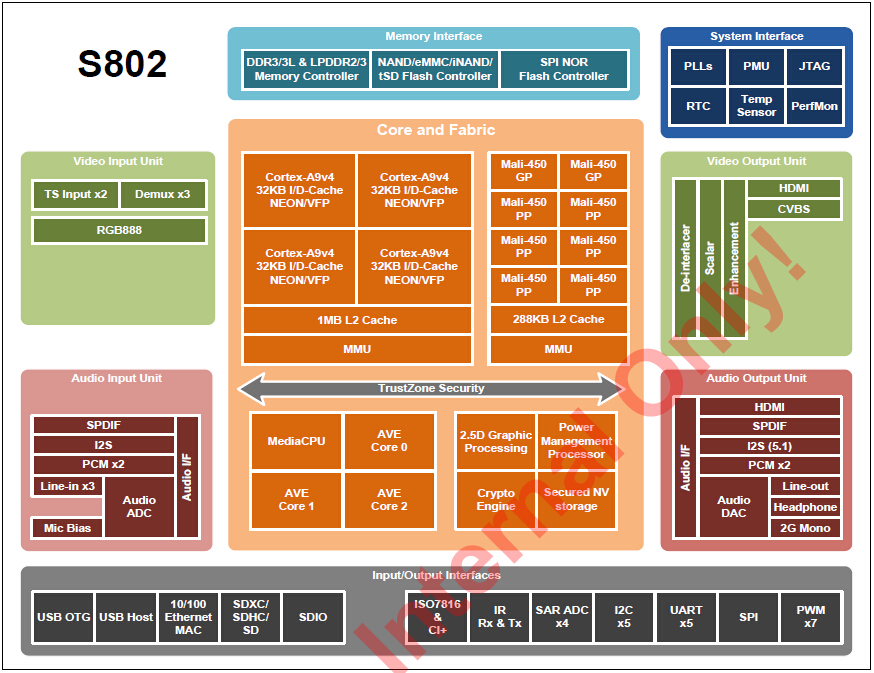

S802 is a quad core ARM Cortex-A9r4 CPU advanced application processor designed for Set Top Box (STB) and high-end media player applications. It integrates a powerful CPU/GPU subsystem, and a secured 4K video CODEC engine with all major peripherals to form the ultimate low power multimedia AP. Θ®ΒψΜςΦ¥Ω…Ή…―·–ΨΤ§œξœΗ–≈œΔΘ©

S802’s Features

1ΓΔCPU Sub-system

-Quad core ARM Cortex-A9r4 CPU up to 2GHz (DVFS) and 20,000DMIPS

-ARMv7 instruction set, multi-issue superscalar, out-of-order architecture with dynamic branch prediction

-32KB instruction cache and 32KB data cache

-1MB Unified L2 cache

- Advanced NEON and VFP co-processor

- Advanced TrustZone security system

- Application based traffic optimization using internal QoS-based switching fabrics

2ΓΔ3D Graphics Processing Unit

- Eight core ARM Mali-450 GPU up to 600MHz+ (DVFS)

- Dual Geometry Processors with 32KB L2 cache

- Six Pixel Processors with 2x 128KB L2 caches

- Concurrent multi-core processing

- 3600Mpix/sec and 132Mtri/sec

- Full scene over-sampled 4X anti-aliasing engine with no additional bandwidth usage

- OpenGL ES 1.1/2.0 and OpenVG 1.1 support

3ΓΔ2.5D Graphics Processor

- Fast bitblt engine with dual inputs and single output

- Programmable raster operations (ROP)

- Programmable polyphase scaling filter

- Supports multiple video formats 4:2:0, 4:2:2 and 4:4:4 and multiple pixel formats (8/16/24/32 bits graphics layer)

- Fast color space conversion

- Advanced anti-flickering filter

4ΓΔCrypto Engine

- Supports AES block cipher with 128/192/256 bits keys, standard 16 bytes block size and streaming ECB, CBC and CTR modes

- Supports DES/3DES block cipher with ECB and CBC modes supporting 64 bits key for DES and 192 bits key for 3DES

- Built-in LSFR Random number generator

5ΓΔVideo/Picture CODEC

- Tri-cores Amlogic Video Engine (AVE) based on scalable multi-core architecture with dedicated hardware decoders an encoders

- Hardware based trusted video path (TVP)

- Supports multiple “secured” video decoding sessions and simultaneous decoding and encoding

- Video/Picture Decoding

- Video/Picture Encoding

6ΓΔVideo Post-Processing Engine

- Motion adaptive 3D noise reduction filter

- Advanced motion adaptive edge enhancing de-interlacing engine

- 3:2 pull-down support

- Programmable poly-phase scalar for both horizontal and vertical dimension for zoom and windowing

- Programmable color management filter (to enhance blue, green, red, face and other colors)

- Dynamic Non-Linear Luma filter

- Programmable color matrix pipeline

- Video mixer: 2 video planes and 2 graphics planes per video output

7ΓΔVideo Output

- Built-in HDMI 1.4b transmitter including both controller and PHY with CEC and HDCP, 4Kx2K@30 max resolution output

-CVBS 480i/576i standard definition output

-Supports all standard SD/HD/UHD video output formats: 480i/p, 576i/p, 720p ,1080i/p and 4Kx2K

- Supports dual video output with combination of CVBS+HDMI

- Supports 3D HDMI display

8ΓΔAudio CODEC and Input/Output

-Low power MediaCPU with DSP audio processing

-Supports MP3, AAC, WMA, RM, FLAC, Ogg and programmable with 5.1 down-mixing

- Internal audio CODEC supporting 3 channels stereo input, 1 channel stereo HP/SPK output and 1 channel 2G mono output

- I2S audio interface supporting 6-channel(5.1) out and 2-channel in

- Built-in SPDIF/IEC958 and PCM serial digital audio input/output

- Supports concurrent dual audio stereo channel output with combination of analog+PCM or I2S+PCM

9ΓΔMemory and Storage Interface

- Dual-channel 32-bit SDRAM memory interface running up to DDR1600

-Supports up to 4GB DDR3, DDR3L, LPDDR2 and LPDDR3 memory

-TrustZone protected DRAM memory region and internal SRAM

- Supports SLC/MLC/TLC NAND Flash with 60-bit ECC, compatible to ONFI 2.1 and Toggle 2.0 mode

-SDSC/SDHC/SDXC card and SDIO interface with 1-bit and 4-bit data bus width supporting spec version 2.x/3.x/4.x DS/HS modes up to UHS-I SDR50

-eMMC and MMC card interface with 1/4/8-bit data bus width supporting spec version 4.4x/4.5x HS200 (up to 100MHz clock), compatible with standard iNAND interface

-Supports serial 1, 2 or 4-bit NOR Flash via SPI interface

-Built-in 4k bits One-Time-Programming ROM for key storage

10ΓΔNetwork

- Integrated IEEE 802.3 10/100 Ethernet controller with RMII interface

- Optional 50MHz clock output to Ethernet PHY

- WiFi/IEEE802.11 & Bluetooth supporting via SDIO/USB/UART/PCM

11ΓΔDigital Television Interface

-Two transport stream(TS) input interfaces with three built-in demux processor for connecting to external digital TV tuner/demodulator and one output TS interface

-Built-in PWM, I2C and SPI interfaces to control tuner and demodulator

I-ntegrated CI+ ports and ISO 7816 smart card controller

12ΓΔIntegrated I/O Controllers and Interfaces

-Dual USB 2.0 high-speed USB I/O, one USB Host and one USB OTG

- 5 UART, 5 I2C and SPI interface with 3 slave selects

-Seven PWMs

-Programmable IR remote input/output controllers

-Built-in 10bit SAR ADC with 4 input channels

- A set of General Purpose IO interfaces with built-in pull up and pull down

13ΓΔSystem, Peripherals and Misc. Interfaces

- Integrated general purpose timers, counters, DMA controllers

-Integrated RTC with battery backup option

- 24 MHz and 32 KHz crystal oscillator input

- Embedded debug interface using ICE/JTAG

14ΓΔPower Management

-Multiple external power domains controlled by PMIC

-Multiple internal power domains controlled by software

- Multiple sleep modes for CPU, system, DRAM, etc.

- Multiple internal PLLs for DVFS operation

-Multi-voltage I/O design for 1.8V and 3.3V

-Power management auxiliary processor in dedicated always-on (AO) power domain to communicate with external PMIC

15ΓΔSecurity

-Trustzone based Trusted Execution Environment (TEE)

-Secured boot, OTP, internal control buses and storage

- Protected memory regions and scrambled memory data interface

- Trusted Video Path and Secured (needs SecureOS software)

16ΓΔPackage

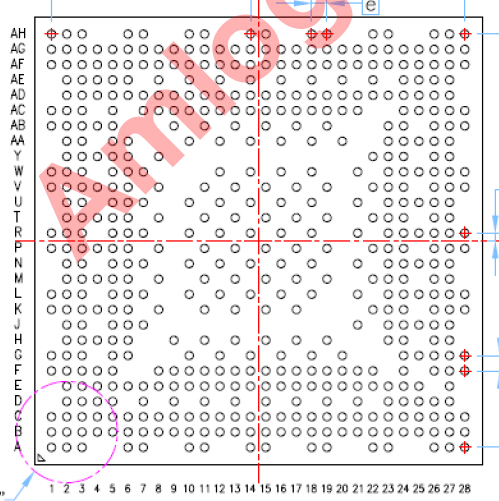

- LFBGA, 19x19mm, 531-ball, 0.65 ball pitch, RoHS compliant

S802’s Block Diagram

S802’s Package

“ΒΈώΈΔ–≈

“ΒΈώΈΔ–≈

’Ϋ¬‘ΚœΉςΈΔ–≈

’Ϋ¬‘ΚœΉςΈΔ–≈

S802.PDF

S802.PDF