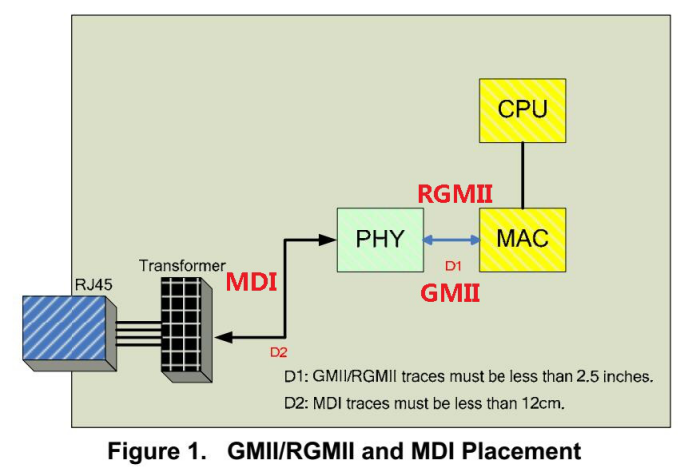

网络通信路径常可总结为:网络数据-->RJ45接口-->网络变压器-->网络PHY芯片-->MAC-->CPU,如图1。其中网络变压器到PHY之前传输接口一般为MDI,而PHY到MAC之前的传输接口一般包括有MII、RMII、SMII、SSMII、SSSMII、GMII、RGMII、SGMII、TBI、RTBI、XGMII、XAUI、XLAUI等,下面我们以RTL8211E为例对网络通信路径接口做一次梳理与总结,桑尼奇孙生,18576699326,QQ:2335804557,欢迎交流!(更多详情)

、

对应于RTL8211E,在物理网线与RTL8211E之间,主要通过MDI接口传输,而对于RTL8211E与MAC之前的通信接口会随RTL8211E的版本不同,会有些许差异,RTL8211E-VB-CG为RGMII接口,而RTL8211EG-VB-CG则是除RGMII接口外还具备MII、GMII接口。

以下则具体介绍这几类接口 :

(1)MDI的全称 Medium Dependent Interface ,网络上给的翻译是介质相关接口。在 hub或 switch 中有两种接口,分别叫 MDI port和 MDI-X port, MDI port 也叫做级联端口( uplink port ),是 hub 或 switch 之间相互连接的端口。 MDI port和 MDI-X port 之间最大的区别在于, MDI port内部发送数据线和接收数据线没交叉,而MDI-X port 内部发送数据线和接收数据线是交叉的,这个X代表交叉的意思。

下图示意了hub或switch内部的结构,transmit代表发送数据线,receive代表接收数据线,两者在内部交叉着。

(2)MII接口

MII是英文Medium Independent Interface的缩写,翻译成中文是“介质独立接口”,该接口一般应用于MAC层和PHY层之间的以太网数据传输,也可叫数据接口。

TXD(Transmit Data)[3:0]:数据发送信号,共4根信号线;

RXD(Receive Data)[3:0]:数据接收信号,共4根信号线;

TX_ER(Transmit Error): 发送数据错误提示信号,同步于TX_CLK,高电平有效,表示TX_ER有效期内传输的数据无效。对于10Mbps速率下,TX_ER不起作用;

RX_ER(Receive Error): 接收数据错误提示信号,同步于RX_CLK,高电平有效,表示RX_ER有效期内传输的数据无效。对于10Mbps速率下,RX_ER不起作用;

TX_EN(Transmit Enable): 发送使能信号,只有在TX_EN有效期内传的数据才有效;

RX_DV(Reveive Data Valid): 接收数据有效信号,作用类型于发送通道的TX_EN;

TX_CLK:发送参考时钟,100Mbps速率下,时钟频率为25MHz,10Mbps速率下,时钟频率为2.5MHz。注意,TX_CLK时钟的方向是从PHY侧指向MAC侧的,因此此时钟是由PHY提供的。

RX_CLK:接收数据参考时钟,100Mbps速率下,时钟频率为25MHz,10Mbps速率下,时钟频率为2.5MHz。RX_CLK也是由PHY侧提供的。

CRS:Carrier Sense,载波侦测信号,不需要同步于参考时钟,只要有数据传输,CRS就有效,另外,CRS只有PHY在半双工模式下有效;

COL:Collision Detectd,冲突检测信号,不需要同步于参考时钟,只有PHY在半双工模式下有效。

MII接口一共有16根线。

(2)RMII接口

RMII即Reduced MII,是MII的简化板,连线数量由MII的16根减少为8根。

TXD[1:0]:数据发送信号线,数据位宽为2,是MII接口的一半;

RXD[1:0]:数据接收信号线,数据位宽为2,是MII接口的一半;

TX_EN(Transmit Enable):数据发送使能信号,与MII接口中的该信号线功能一样;

RX_ER(Receive Error):数据接收错误提示信号,与MII接口中的该信号线功能一样;

CLK_REF:是由外部时钟源提供的50MHz参考时钟,与MII接口不同,MII接口中的接收时钟和发送时钟是分开的,而且都是由PHY芯片提供给MAC芯片的。这里需要注意的是,由于数据接收时钟是由外部晶振提供而不是由载波信号提取的,所以在PHY层芯片内的数据接收部分需要设计一个FIFO,用来协调两个不同的时钟,在发送接收的数据时提供缓冲。PHY层芯片的发送部分则不需要FIFO,它直接将接收到的数据发送到MAC就可以了。

CRS_DV:此信号是由MII接口中的RX_DV和CRS两个信号合并而成。当介质不空闲时,CRS_DV和RE_CLK相异步的方式给出。当CRS比RX_DV早结束时(即载波消失而队列中还有数据要传输时),就会出现CRS_DV在半位元组的边界以25MHz/2.5MHz的频率在0、1之间的来回切换。因此,MAC能够从 CRS_DV中精确的恢复出RX_DV和CRS。

在100Mbps速率时,TX/RX每个时钟周期采样一个数据;在10Mbps速率时,TX/RX每隔10个周期采样一个数据,因而TX/RX数据需要在数据线上保留10个周期,相当于一个数据发送10次。

当PHY层芯片收到有效的载波信号后,CRS_DV信号变为有效,此时如果FIFO中还没有数据,则它会发送出全0的数据给MAC,然后当FIFO中填入有效的数据帧,数据帧的开头是“101010---”交叉的前导码,当数据中出现“01”的比特时,代表正式数据传输开始,MAC芯片检测到这一变化,从而开始接收数据。

当外部载波信号消失后,CRS_DV会变为无效,但如果FIFO中还有数据要发送时,CRS_DV在下一周期又会变为有效,然后再无效再有效,直到FIFO中数据发送完为止。在接收过程中如果出现无效的载波信号或者无效的数据编码,则RX_ER会变为有效,表示物理层芯片接收出错。

(3)GMII接口

与MII接口相比,GMII的数据宽度由4位变为8位,GMII接口中的控制信号如TX_ER、TX_EN、RX_ER、RX_DV、CRS和COL的作用同MII接口中的一样,发送参考时钟GTX_CLK和接收参考时钟RX_CLK的频率均为125MHz(1000Mbps/8=125MHz)。

在这里有一点需要特别说明下,那就是发送参考时钟GTX_CLK,它和MII接口中的TX_CLK是不同的,MII接口中的TX_CLK是由PHY芯片提供给MAC芯片的,而GMII接口中的GTX_CLK是由MAC芯片提供给PHY芯片的。两者方向不一样。

在实际应用中,绝大多数GMII接口都是兼容MII接口的,所以,一般的GMII接口都有两个发送参考时钟:TX_CLK和GTX_CLK(两者的方向是不一样的,前面已经说过了),在用作MII模式时,使用TX_CLK和8根数据线中的4根。

(4)RGMII接口

RGMII即Reduced GMII,是GMII的简化版本,将接口信号线数量从24根减少到14根(COL/CRS端口状态指示信号,这里没有画出),时钟频率仍旧为125MHz,TX/RX数据宽度从8为变为4位,为了保持1000Mbps的传输速率不变,RGMII接口在时钟的上升沿和下降沿都采样数据。在参考时钟的上升沿发送GMII接口中的TXD[3:0]/RXD[3:0],在参考时钟的下降沿发送GMII接口中的TXD[7:4]/RXD[7:4]。RGMI同时也兼容100Mbps和10Mbps两种速率,此时参考时钟速率分别为25MHz和2.5MHz。

TX_EN信号线上传送TX_EN和TX_ER两种信息,在TX_CLK的上升沿发送TX_EN,下降沿发送TX_ER;同样的,RX_DV信号线上也传送RX_DV和RX_ER两种信息,在RX_CLK的上升沿发送RX_DV,下降沿发送RX_ER。

桑尼奇专业供应网络芯片,涉及USB转RJ45芯片、千兆网络PHY芯片、百兆网络PHY芯片、千兆/百兆网络集线器芯片等,涵盖有Realtek、ICplus、TI、SMSC、Micrel等品牌,具本型号有RTL8152B/RTL8153B,RTL8211E、RTL8211F、RTL8201CP、RTL8201F、IP101GR、DP83848、LAN8720等,可提供样品或型号推荐,欢迎咨询。桑尼奇孙生:18576699326,QQ:2335804557.

(以上信息由深圳市桑尼奇科技有限公司提供)

评论列表: